# Simulation of dynamically structured systems in a model-based system engineering approach applied to reconfigurable hardware

Min Zhu

# ► To cite this version:

Min Zhu. Simulation of dynamically structured systems in a model-based system engineering approach applied to reconfigurable hardware. Computer science. Université Toulouse 3 Paul Sabatier (UT3 Paul Sabatier), 2018. English. NNT: . tel-01938154

# HAL Id: tel-01938154 https://laas.hal.science/tel-01938154

Submitted on 28 Nov 2018

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés. Université Fédérale

En vue de l'obtention du

# DOCTORAT DE L'UNIVERSITÉ FÉDÉRALE TOULOUSE MIDI-PYRÉNÉES

Délivré par :

l'Université Toulouse 3 Paul Sabatier (UT3 Paul Sabatier)

Présentée et soutenue le 1/10/2018 par : MIN ZHU

Simulation de systèmes à structure dynamique dans une approche d'ingénierie système basée modèles appliquée au matériel reconfigurable

## JURY

M. VINCENT ALBERT M. CLÉMENT FOUCHER MME. CLAUDIA FRYDMAN M. FABRICE MULLER M. ALEXANDRE NKETSA M. SÉBASTIEN PILLEMENT Université Toulouse III Université Toulouse III Université Aix-Marseille III Université Nice Sophia Antipolis Université Toulouse III Université de Nantes Examinateur Directeur de thèse Rapporteuse Examinateur Directeur de thèse Rapporteur

## École doctorale et spécialité :

EDSYS : Informatique 4200018 Double mention : EDSYS : Systèmes embarqués 4200046 Unité de Recherche : Laboratoire d'analyse et d'architecture des systèmes Directeurs de Thèse : Monsieur Clément FOUCHER et Monsieur Alexandre NKETSA Rapporteurs : Madame Claudia FRYDMAN et Monsieur Sébastien PILLEMENT

Scientists are not dependent on the ideas of a single man, but on the combined wisdom of thousands of men, all thinking of the same problem, and each doing his little bit to add to the great structure of knowledge which is gradually being erected.

Ernest Rutherford

# Acknowledgements

This thesis represents the final report of my time spent at *System Engineering* and *Integration* team of *Crucial Computing* department at *Laboratory for Analysis and Architecture of Systems*, Toulouse. I would like to take the opportunity to thank many of the people who have supported this thesis and influenced the creation of this work.

I am deeply grateful to Prof. Alexandre NKETSA, for his open-mindedness and critical advice during the discussions. I am very thankful to Clément FOUCHER, for giving constructive guidance thoughout and being an exemplar of a professional researcher. I also would like to specially thank Vincent ALBERT, for passing on his wisdom during the model construction. Their help and supervision made this piece of work possible.

I give full appreciation to Prof. Claudia FRYDMAN and Prof. Sébastien PILLEMENT, for their interest in my work and for refereeing this thesis.

I would like to thank to Philippe ESTEBAN, who took me into this adventure of scientific research after my Master studies of real-time system engineering and stood by me during my three years teaching assistance work. Thank to Hamid DEMMOU for his team leads which make my international presentation possible. Thanks also to Claude BARON for her excellent team building.

I would like to thank all my colleagues at faculté sciences et ingenierie at université Paul Sabatier. Thanks to Emmanuel Montseny for all the preparation made for the practice of Matlab/Simulink. I have shared lots of good moment with the others, especially thanks to the every year Circus.

I would like to give a special thanks to Hélène THIRION, Christèle MOUCLIER, Layla MOURCHID and Catherine GUERIN for their ongoing administrative support and for always giving a helping hand.

This thesis would not be possible without the support of families and friends, without the happiness they brought, sharing cafe culture, music, and good times spent outside of research in Finland, in Mexico, in Portugal, in China. Thank you for your great efforts people around me! Sylvain, David, Diego, Xue Rui, Karla, Guillaume, Yi Xin, Lily, Sangeeth, Yassine, Adina, Daniel et Julie, Violaine et Rémi, He Yun, Wang Rui, for all your emotional support and just being there when I need you.

In the end, I would like to give some very special thanks to the international exchange program ERASMUS, with whom I finished my undergraduate studies in France, and without whom I could not have achieved what I have today.

### Abstract:

As partially reconfigurable technologies develop for embedded systems, the need for a proper model to describe its behavior emerges. Most academic and industrial tools available on the market does not address dynamic structure modeling. The arising of discrete-event modeling, in particular, Discrete Event System Specification (DEVS), propose formal tools for representing and simulating models. DEVS has already extension which handles the dynamic structure modeling. However, the capacities of these existing formalism have limitations. Notably, they do not address the components context aspect.

Also, the existing formalisms have not integrated the system engineering approach. System engineering brings beneficial procedures, notably modeldriven architecture which proposes to separate the system description from its execution target. A platform-specific model is formed from a platformdescription model coupled with a platform independent model.

To address these needs, we propose a model description formalism which takes into consideration these two aspects: dynamic structure modeling and system engineering. This formalism is based on DEVS and called Partially Reconfigurable Discrete Event System Specification (PRDEVS). PRDEVS allows to represent dynamic-structure models independently from the simulation platform.

The presented approach can be applied to different types of targets, such as software and reconfigurable hardware. This thesis addresses these two kinds of platforms, demonstrating the suitability of the abstract formalism to actual platforms.

**Keywords:** Reconfigurable hardware systems, Modeling, Discrete event simulation, Model-based system engineering, Model-driven architecture

### Résumé :

Avec l'évolution des techniques de reconfiguration partielle pour les systèmes embarqués, le besoin d'un modèle de description capable de représenter ces comportements émerge. La plupart des outils disponibles sur le marché, tant académiques qu'industriels, ne prennent pas en compte la modélisation des systèmes à structure dynamique. L'émergence de la modélisation à évènements discrets, notamment Discrete Event System Specification (DEVS), propose des outils formels pour représenter et simuler des modèles. DEVS propose déjà des extensions capable de prendre en compte la modélisation à structure dynamique. Néanmoins, les possibilités offertes par ces extensions rencontrent certaines limites. En particulier, elles ne proposent pas de moyen de gérer l'aspect contexte des composants.

De plus, les formalismes existants n'ont pas intégré l'approche ingénierie système. L'ingénierie système met en place des procédures intéressantes, notamment l'architecture dirigée par les modèles, qui propose de séparer la description du système de sa plateforme d'exécution. Un modèle spécifique à une plateforme est ainsi la résultante d'un modèle de description de la plateforme combiné avec un modèle d'application indépendant de toute plateforme.

Pour répondre à ces besoins, nous proposons un formalisme de description de modèles prenant en compte ces deux aspects : la modélisation à structure dynamique, et l'ingénierie système. Ce formalisme est basé sur DEVS, et nommé Partially Reconfigurable Discrete Event System Specification (PRDEVS). PRDEVS permet de représenter les modèles à structure dynamique indépendamment de la plateforme de simulation.

L'approche présentée peut être appliquée à différents types de cibles, tels le logiciel et le matériel reconfigurable. Cette thèse présente des mises en œuvre du formalisme abstrait sur ces deux types de plateformes, démontrant ainsi sa capacité à être déployé sur des plateformes réelles.

**Mots clés :** Systèmes matériels reconfigurables, Modélisation, Simulation à évènements discrets, Ingénierie système basée modèles, Architecture dirigée par les modèles

# Contents

| In       | Introduction 1                                                  |                                                                                                |                                                          |                                                    |  |  |

|----------|-----------------------------------------------------------------|------------------------------------------------------------------------------------------------|----------------------------------------------------------|----------------------------------------------------|--|--|

| 1        | Scie                                                            | entific                                                                                        | context & state of the art                               | 7                                                  |  |  |

|          | 1.1                                                             | Syster                                                                                         | n engineering and simulation                             | 9                                                  |  |  |

|          |                                                                 | 1.1.1                                                                                          | Systems and system engineering                           | 9                                                  |  |  |

|          |                                                                 | 1.1.2                                                                                          | Modeling and simulation                                  | 11                                                 |  |  |

|          |                                                                 | 1.1.3                                                                                          | Model-Driven Architecture                                | 12                                                 |  |  |

|          |                                                                 | 1.1.4                                                                                          | Syntax and semantics                                     | 13                                                 |  |  |

|          | 1.2                                                             | DEVS                                                                                           | and its extensions                                       | 14                                                 |  |  |

|          |                                                                 | 1.2.1                                                                                          | Discrete Event System Specification                      | 14                                                 |  |  |

|          |                                                                 | 1.2.2                                                                                          | Dynamic Structure DEVS and its parallel version $\ldots$ | 18                                                 |  |  |

|          |                                                                 | 1.2.3                                                                                          | Dynamic DEVS and its dynamic port extension              | 23                                                 |  |  |

|          |                                                                 | 1.2.4                                                                                          | Synthesizable DEVS                                       | 26                                                 |  |  |

|          |                                                                 | 1.2.5                                                                                          | Reconfigurable DEVS                                      | 27                                                 |  |  |

|          | 1.3                                                             | Dynar                                                                                          | mically reconfigurable computing systems                 | 29                                                 |  |  |

|          |                                                                 | 1.3.1                                                                                          | Programmable logic device                                | 30                                                 |  |  |

|          |                                                                 | 1.3.2                                                                                          | Partial reconfiguration                                  | 31                                                 |  |  |

|          | 1.4                                                             | Concl                                                                                          | usion $\ldots$                                           | 33                                                 |  |  |

| <b>2</b> | Partially Reconfigurable Discrete Event System Specification 33 |                                                                                                |                                                          |                                                    |  |  |

| 2        | <b>1 a</b><br>2.1                                               | -                                                                                              | EVS meta-model syntax                                    | <b>35</b><br>36                                    |  |  |

|          | 2.1                                                             | 2.1.1                                                                                          | PRDEVS abstract syntax                                   | 36                                                 |  |  |

|          |                                                                 | 2.1.1<br>2.1.2                                                                                 |                                                          | - 50                                               |  |  |

|          |                                                                 |                                                                                                | Boot PBDEVS component                                    | 37                                                 |  |  |

|          |                                                                 |                                                                                                | Root PRDEVS component                                    | 37<br>38                                           |  |  |

|          |                                                                 | 2.1.3                                                                                          | Coupled components                                       | 38                                                 |  |  |

|          |                                                                 | 2.1.3<br>2.1.4                                                                                 | Coupled components                                       | $\frac{38}{38}$                                    |  |  |

|          |                                                                 | $2.1.3 \\ 2.1.4 \\ 2.1.5$                                                                      | Coupled components                                       | 38<br>38<br>39                                     |  |  |

|          | 0.0                                                             | $2.1.3 \\ 2.1.4 \\ 2.1.5 \\ 2.1.6$                                                             | Coupled components                                       | 38<br>38<br>39<br>39                               |  |  |

|          | 2.2                                                             | 2.1.3<br>2.1.4<br>2.1.5<br>2.1.6<br>PRDE                                                       | Coupled components                                       | 38<br>38<br>39<br>39<br>40                         |  |  |

|          | 2.2                                                             | 2.1.3<br>2.1.4<br>2.1.5<br>2.1.6<br>PRDE<br>2.2.1                                              | Coupled components                                       | 38<br>38<br>39<br>39<br>40<br>41                   |  |  |

|          | 2.2                                                             | 2.1.3<br>2.1.4<br>2.1.5<br>2.1.6<br>PRDE<br>2.2.1<br>2.2.2                                     | Coupled components                                       | 38<br>38<br>39<br>39<br>40<br>41<br>42             |  |  |

|          |                                                                 | 2.1.3<br>2.1.4<br>2.1.5<br>2.1.6<br>PRDE<br>2.2.1<br>2.2.2<br>2.2.3                            | Coupled components                                       | 38<br>38<br>39<br>39<br>40<br>41<br>42<br>44       |  |  |

|          | 2.2<br>2.3                                                      | 2.1.3<br>2.1.4<br>2.1.5<br>2.1.6<br>PRDE<br>2.2.1<br>2.2.2<br>2.2.3<br>Graph                   | Coupled components                                       | 38<br>38<br>39<br>39<br>40<br>41<br>42<br>44<br>45 |  |  |

|          |                                                                 | 2.1.3<br>2.1.4<br>2.1.5<br>2.1.6<br>PRDE<br>2.2.1<br>2.2.2<br>2.2.3<br>Graph<br>2.3.1          | Coupled components                                       | 38<br>38<br>39<br>40<br>41<br>42<br>44<br>45<br>46 |  |  |

|          |                                                                 | 2.1.3<br>2.1.4<br>2.1.5<br>2.1.6<br>PRDE<br>2.2.1<br>2.2.2<br>2.2.3<br>Graph<br>2.3.1<br>2.3.2 | Coupled components                                       | 38<br>38<br>39<br>39<br>40<br>41<br>42<br>44<br>45 |  |  |

| 3 | A s                                                            | oftwar                                                                                                                                        | e PDM for the PRDEVS PIM                          | 53                                                                         |

|---|----------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|----------------------------------------------------------------------------|

|   | 3.1                                                            | Platfo                                                                                                                                        | rm study                                          | 54                                                                         |

|   |                                                                | 3.1.1                                                                                                                                         | Software platform and object-oriented programming | 55                                                                         |

|   |                                                                | 3.1.2                                                                                                                                         | A quick look into a software simulator core       | 55                                                                         |

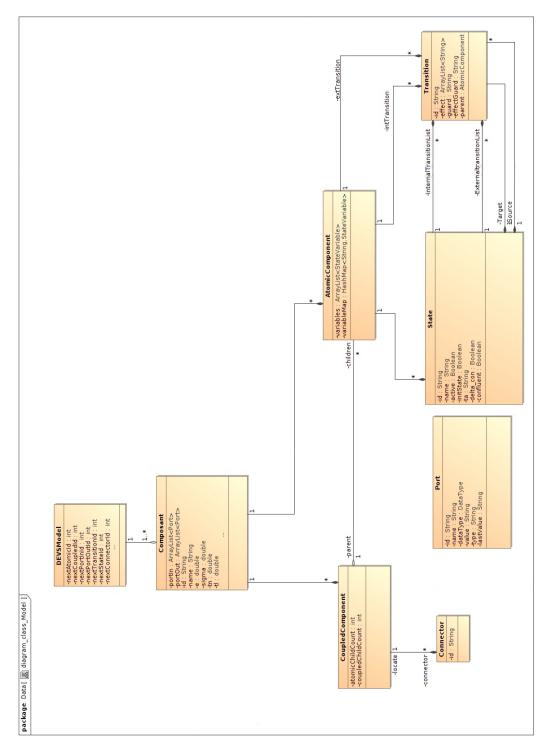

|   | 3.2                                                            | Hierar                                                                                                                                        | chy of the software PDM                           | 60                                                                         |

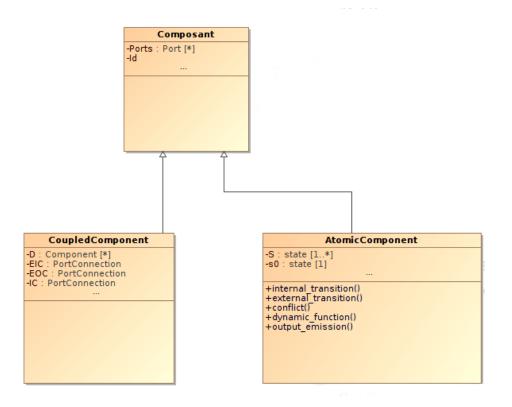

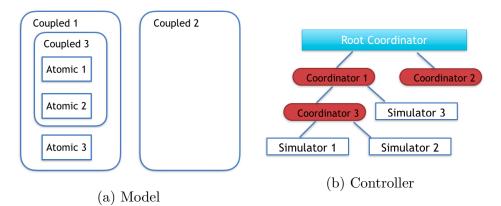

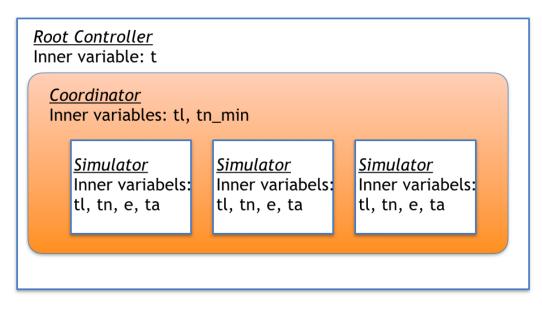

|   |                                                                | 3.2.1                                                                                                                                         | Atomic/coupled component                          | 60                                                                         |

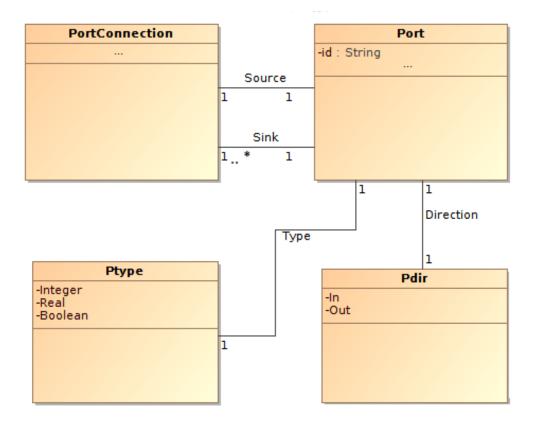

|   |                                                                | 3.2.2                                                                                                                                         | Port/connector                                    | 61                                                                         |

|   | 3.3                                                            | Mappi                                                                                                                                         | ing and realization of the PDM                    | 62                                                                         |

|   |                                                                | 3.3.1                                                                                                                                         | Meta model transformation for time                | 64                                                                         |

|   |                                                                | 3.3.2                                                                                                                                         | Input/output message bags                         | 64                                                                         |

|   |                                                                | 3.3.3                                                                                                                                         | Dynamic functions calls                           | 65                                                                         |

|   |                                                                | 3.3.4                                                                                                                                         | Time advance (Ta)                                 | 65                                                                         |

|   |                                                                | 3.3.5                                                                                                                                         | Imminent time $(Tn_min)$                          | 65                                                                         |

|   |                                                                | 3.3.6                                                                                                                                         | Last event time $(Tl)$                            | 66                                                                         |

|   |                                                                | 3.3.7                                                                                                                                         | Elapsed time (e)                                  | 66                                                                         |

|   | 3.4                                                            | Case s                                                                                                                                        | study: a PSM test                                 | 67                                                                         |

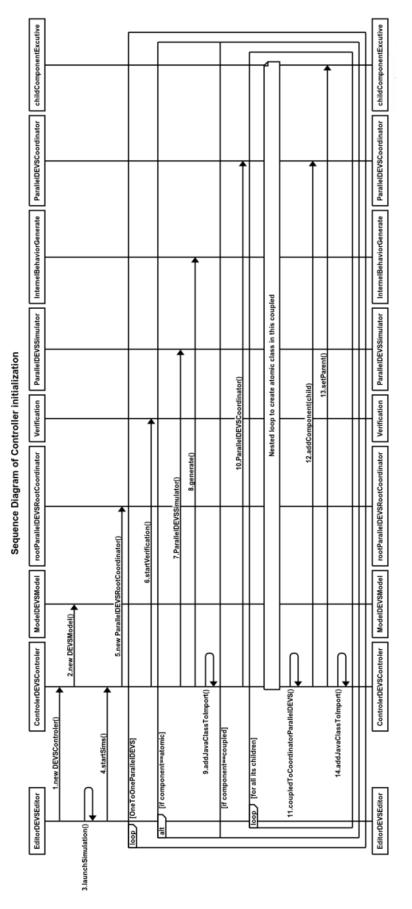

|   |                                                                | 3.4.1                                                                                                                                         | Initialization of the model                       | 69                                                                         |

|   |                                                                | 3.4.2                                                                                                                                         | Simulation                                        | 70                                                                         |

|   | 3.5                                                            | Conclu                                                                                                                                        | usion                                             | 70                                                                         |

| 4 | An                                                             | hardw                                                                                                                                         | are FPGA PDM for the PRDEVS PIM                   | 73                                                                         |

| 4 |                                                                |                                                                                                                                               |                                                   |                                                                            |

|   | 4.1                                                            | PDM                                                                                                                                           | architecture: a high-level view                   | 74                                                                         |

|   | $4.1 \\ 4.2$                                                   |                                                                                                                                               | architecture: a high-level view                   |                                                                            |

|   |                                                                | Sched                                                                                                                                         | uling and temporal aspects                        | 78                                                                         |

|   | 4.2                                                            | Sched                                                                                                                                         |                                                   | 74<br>78<br>79<br>79                                                       |

|   | 4.2                                                            | Sched<br>Comp                                                                                                                                 | uling and temporal aspects                        | 78<br>79                                                                   |

|   | 4.2                                                            | Sched<br>Comp<br>4.3.1                                                                                                                        | uling and temporal aspects                        | 78<br>79<br>79<br>81                                                       |

|   | 4.2                                                            | Sched<br>Comp<br>4.3.1<br>4.3.2                                                                                                               | uling and temporal aspects                        | 78<br>79<br>79<br>81<br>82                                                 |

|   | 4.2                                                            | Schede<br>Comp<br>4.3.1<br>4.3.2<br>4.3.3<br>4.3.4                                                                                            | uling and temporal aspects                        | 78<br>79<br>79<br>81<br>82<br>84                                           |

|   | 4.2<br>4.3                                                     | Schede<br>Comp<br>4.3.1<br>4.3.2<br>4.3.3<br>4.3.4                                                                                            | uling and temporal aspects                        | 78<br>79<br>79<br>81<br>82<br>84<br>84                                     |

|   | 4.2<br>4.3                                                     | Schede<br>Comp<br>4.3.1<br>4.3.2<br>4.3.3<br>4.3.4<br>Atomi<br>4.4.1                                                                          | uling and temporal aspects                        | 78<br>79<br>79<br>81<br>82<br>84<br>84<br>85                               |

|   | 4.2<br>4.3                                                     | Schede<br>Comp<br>4.3.1<br>4.3.2<br>4.3.3<br>4.3.4<br>Atomi<br>4.4.1<br>4.4.2                                                                 | uling and temporal aspects                        | 78<br>79<br>79<br>81<br>82<br>84<br>84<br>85<br>86                         |

|   | 4.2<br>4.3                                                     | Schede<br>Comp<br>4.3.1<br>4.3.2<br>4.3.3<br>4.3.4<br>Atomi<br>4.4.1<br>4.4.2<br>4.4.3                                                        | uling and temporal aspects                        | 78<br>79<br>79<br>81<br>82<br>84<br>84<br>85<br>86<br>87                   |

|   | 4.2<br>4.3                                                     | Schede<br>Comp<br>4.3.1<br>4.3.2<br>4.3.3<br>4.3.4<br>Atomi<br>4.4.1<br>4.4.2<br>4.4.3<br>4.4.4                                               | uling and temporal aspects                        | 78<br>79<br>79<br>81<br>82<br>84<br>84<br>85<br>86<br>87<br>88             |

|   | <ul><li>4.2</li><li>4.3</li><li>4.4</li></ul>                  | Schede<br>Comp<br>4.3.1<br>4.3.2<br>4.3.3<br>4.3.4<br>Atomi<br>4.4.1<br>4.4.2<br>4.4.3<br>4.4.4<br>4.4.5                                      | uling and temporal aspects                        | 78<br>79<br>81<br>82<br>84<br>84<br>85<br>86<br>87<br>88<br>89             |

|   | 4.2<br>4.3                                                     | Schede<br>Comp<br>4.3.1<br>4.3.2<br>4.3.3<br>4.3.4<br>Atomi<br>4.4.1<br>4.4.2<br>4.4.3<br>4.4.4<br>4.4.5<br>SC fur                            | uling and temporal aspects                        | 78<br>79<br>81<br>82<br>84<br>84<br>85<br>86<br>87<br>88<br>89<br>90       |

|   | <ul><li>4.2</li><li>4.3</li><li>4.4</li></ul>                  | Schede<br>Comp<br>4.3.1<br>4.3.2<br>4.3.3<br>4.3.4<br>Atomi<br>4.4.1<br>4.4.2<br>4.4.3<br>4.4.4<br>4.4.5<br>SC fun<br>4.5.1                   | uling and temporal aspects                        | 78<br>79<br>81<br>82<br>84<br>85<br>86<br>87<br>88<br>89<br>90<br>91       |

|   | <ul> <li>4.2</li> <li>4.3</li> <li>4.4</li> <li>4.5</li> </ul> | Schede<br>Comp<br>4.3.1<br>4.3.2<br>4.3.3<br>4.3.4<br>Atomi<br>4.4.1<br>4.4.2<br>4.4.3<br>4.4.4<br>4.4.5<br>SC fun<br>4.5.1<br>4.5.2          | uling and temporal aspects                        | 78<br>79<br>81<br>82<br>84<br>85<br>86<br>87<br>88<br>89<br>90<br>91<br>92 |

|   | <ul><li>4.2</li><li>4.3</li><li>4.4</li></ul>                  | Schedy<br>Comp<br>4.3.1<br>4.3.2<br>4.3.3<br>4.3.4<br>Atomi<br>4.4.1<br>4.4.2<br>4.4.3<br>4.4.4<br>4.4.5<br>SC fun<br>4.5.1<br>4.5.2<br>Examp | uling and temporal aspects                        | 78<br>79<br>79<br>81<br>82                                                 |

# Bibliography

105

# List of Figures

| 1.1        | MDA structure of a meta-model                                                                                                                             |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

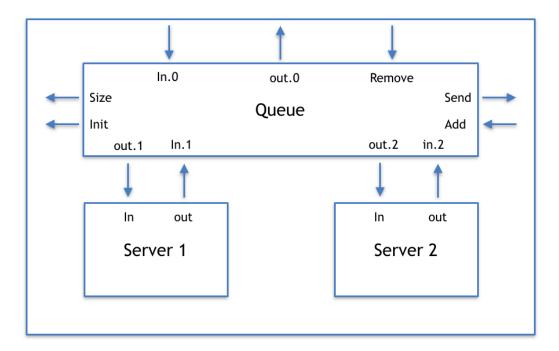

| 1.2        | A DSDEVS exemple: block diagram of a node                                                                                                                 |

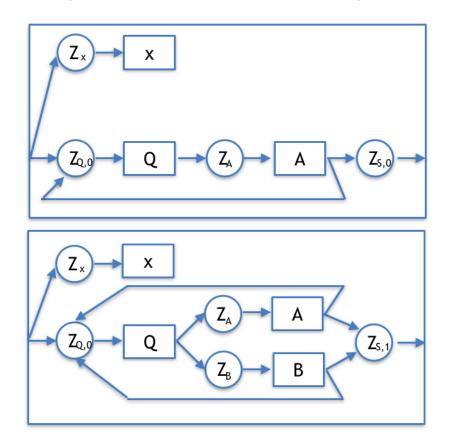

| 1.3        | A DSDE exemple: one server network change to two sever net-                                                                                               |

|            | work                                                                                                                                                      |

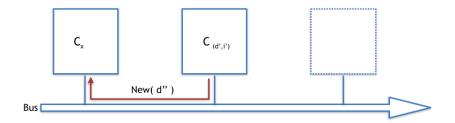

| 1.4        | A RecDEVS exemple: add a new component                                                                                                                    |

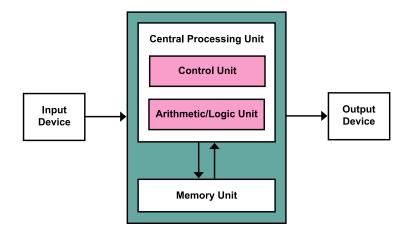

| 1.5        | Von Neumann architecture                                                                                                                                  |

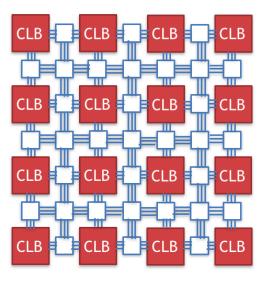

| 1.6        | FPGA architecture                                                                                                                                         |

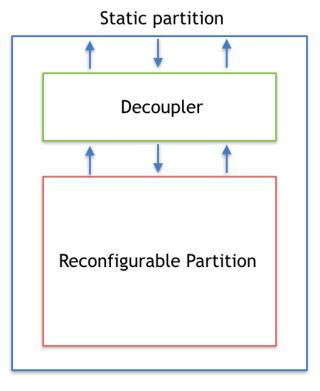

| 1.7        | Virtual socket containing a decoupler                                                                                                                     |

|            |                                                                                                                                                           |

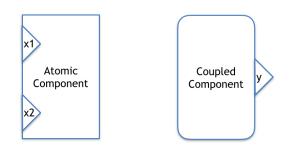

| 2.1        | Graphic representation of components                                                                                                                      |

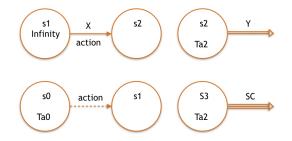

| 2.2        | Graphic presentation of transitions                                                                                                                       |

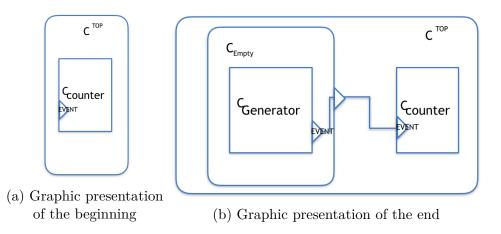

| 2.3        | Graphic presentation of the top level component                                                                                                           |

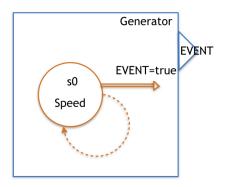

| 2.4        | Graphic presentation of the generator                                                                                                                     |

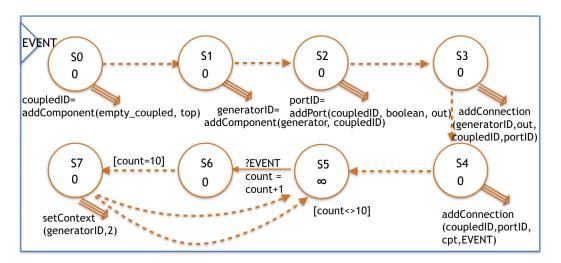

| 2.5        | Graphic presentation of the counter                                                                                                                       |

| 0.1        |                                                                                                                                                           |

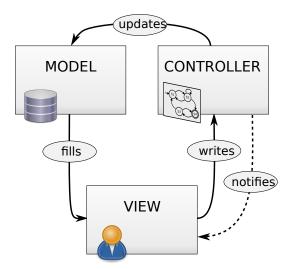

| 3.1        | MVC Process                                                                                                                                               |

| 3.2        | Class diagram of Model package                                                                                                                            |

| 3.3        | Sequence diagram of controller initialization                                                                                                             |

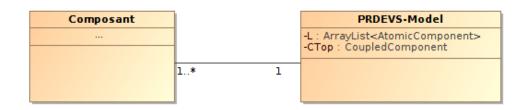

| 3.4        | PRDEVS UML representation                                                                                                                                 |

| 3.5        | Components UML representation                                                                                                                             |

| 3.6        | Port and PortConnection types UML representation 62                                                                                                       |

| 3.7        | One-to-one correspondence                                                                                                                                 |

| 3.8        | Time variable in the different objects                                                                                                                    |

| 3.9        | Moving Rules for players                                                                                                                                  |

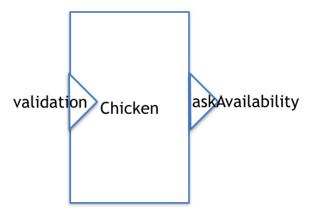

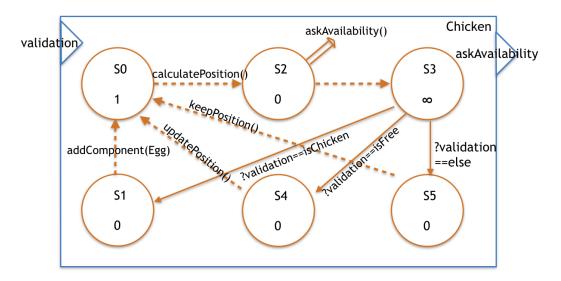

| 3.10       | External view of chicken                                                                                                                                  |

|            | Internal view state machine of chicken                                                                                                                    |

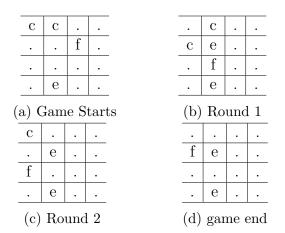

|            | Example of a game turn 69                                                                                                                                 |

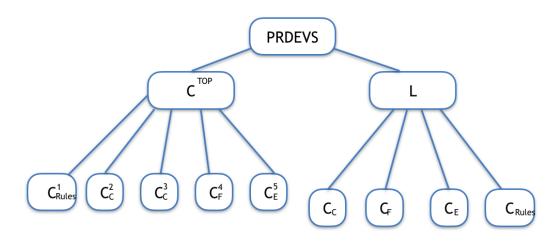

| 3.13       | Tree view of model $\ldots \ldots \ldots$ |

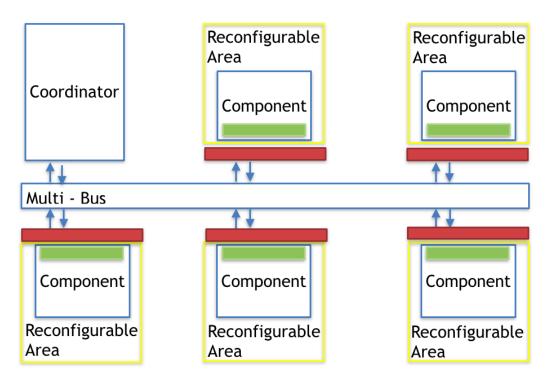

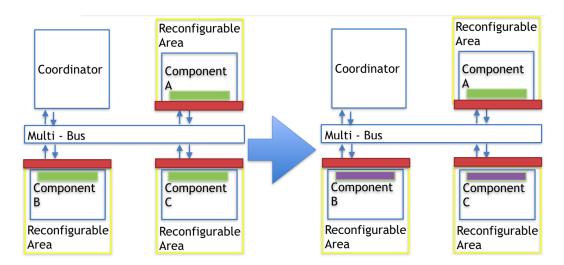

| 4.1        | Global view of PSM                                                                                                                                        |

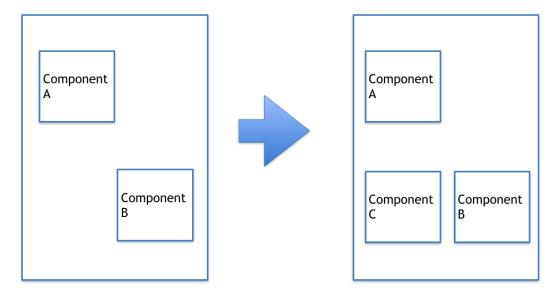

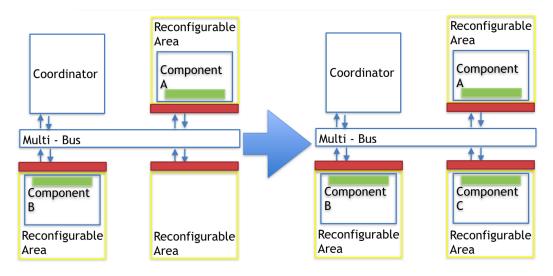

|            | Example of addComponent into the circuit                                                                                                                  |

| 4.3        | Architecture of a new component added                                                                                                                     |

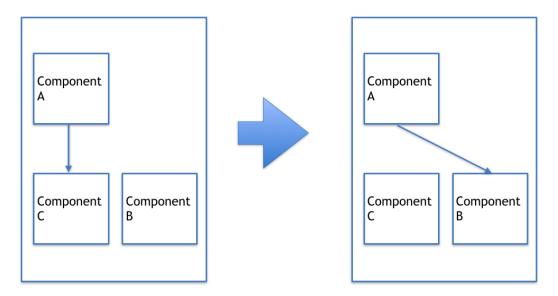

| 4.4        | Example of a connection change                                                                                                                            |

| 4.4        | Architecture of a connection change                                                                                                                       |

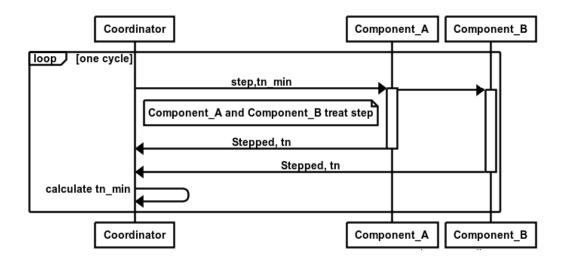

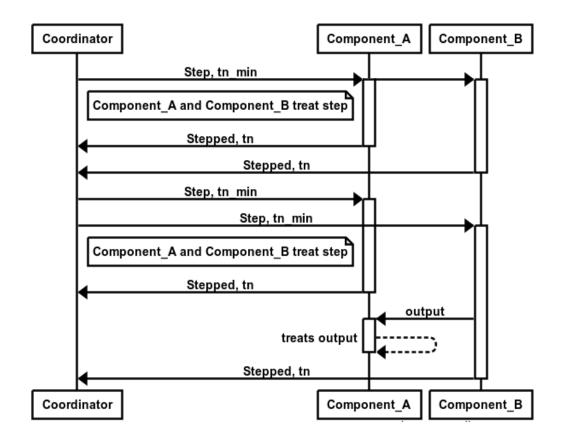

| 4.6        | General simulation cycle                                                                                                                                  |

| 4.0<br>4.7 | Example of communication between two components 80                                                                                                        |

| 4.7        |                                                                                                                                                           |

|            |                                                                                                                                                           |

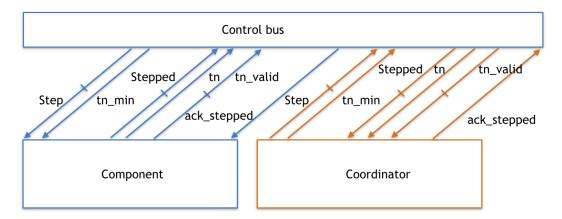

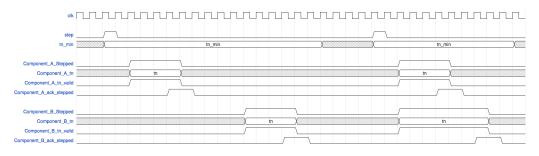

| 4.9        | Wave of a cycle of Step under control bus 81                                                                                                              |

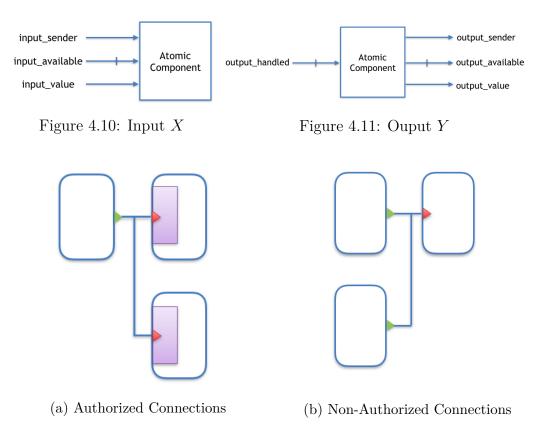

| 4.10 | Input $X$                                                                                                                                |

|------|------------------------------------------------------------------------------------------------------------------------------------------|

| 4.11 | Ouput $Y \ldots $ |

| 4.12 | Connections between components                                                                                                           |

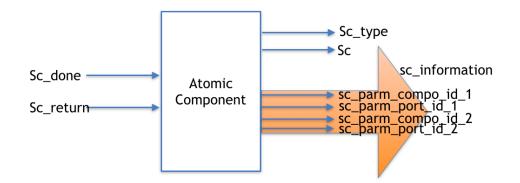

| 4.13 | Dynamic calls extra ports                                                                                                                |

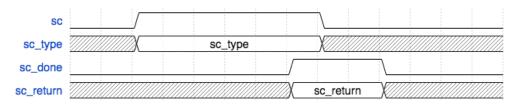

| 4.14 | Wave of a cycle of Step                                                                                                                  |

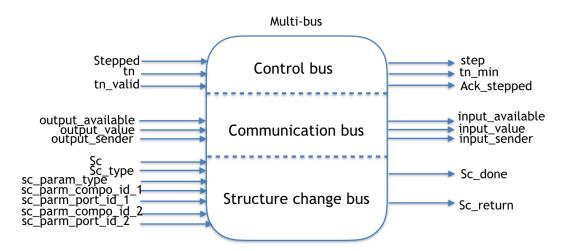

| 4.15 | Multi-bus structure                                                                                                                      |

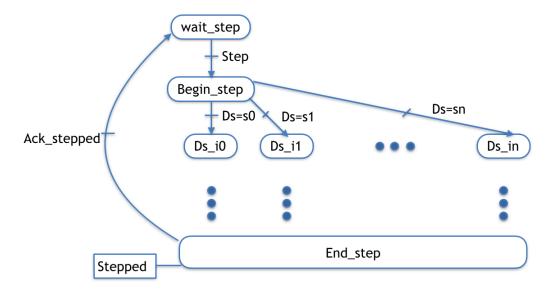

| 4.16 | General state machine                                                                                                                    |

| 4.17 | DEVS model of an internal transition                                                                                                     |

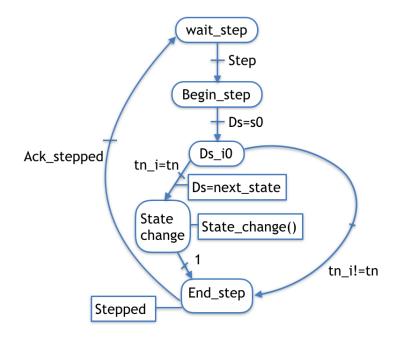

| 4.18 | Internal transition                                                                                                                      |

| 4.19 | DEVS model of an external transition                                                                                                     |

| 4.20 | External transition                                                                                                                      |

| 4.21 | DEVS model of an output emission                                                                                                         |

| 4.22 | Output emission                                                                                                                          |

| 4.23 | Non-conflict transition                                                                                                                  |

| 4.24 | Conflict transition                                                                                                                      |

| 4.25 | DEVS model of a structure change emission 90                                                                                             |

| 4.26 | Dynamic transition: addComponent                                                                                                         |

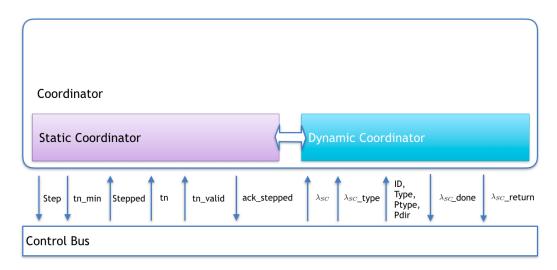

| 4.27 | Coordinator                                                                                                                              |

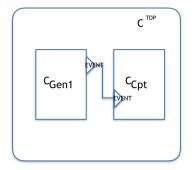

| 4.28 | Graphic presentation of the example                                                                                                      |

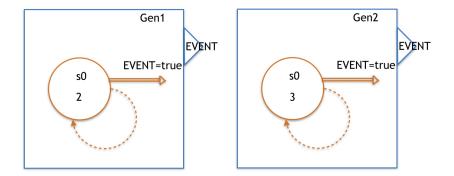

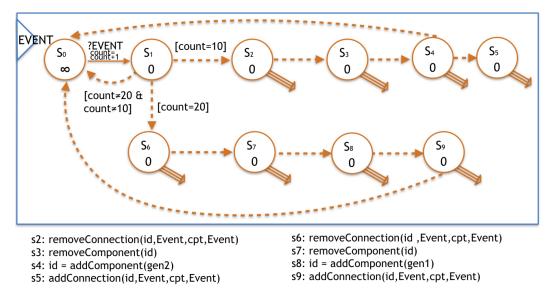

| 4.29 | Graphic presentation of the generator                                                                                                    |

| 4.30 | Graphic presentation of the counter                                                                                                      |

# Introduction

Mankind has created tools of all kinds to accomplish those tasks which are difficult to achieve directly by our own hands. The ambitions of human beings, together with these technologies, make it possible to fly and travel into space. However, the creation of a new system is generally not as straightforward as it might seem.

Human-made systems, from vehicles to satellites, interact with their environments. The interactions between a system and its surrounding lead to different additional performance factors. The environment impacts the system properties. At the same time, the system can change its environment. For example, aircrafts lift comes from the air and the acceleration of the aircraft is limited by the air resistance at the same time. Building a system requires a full-scale consideration of all such possible interactions.

Nowadays, the creation of an artificial system is sometimes so complex that it involves interdisciplinary expert cooperation. Such a complexity makes it difficult to estimate the delays, the costs, and even feasibility. Moreover, the development of a new product can take several years. A bigger team and a longer process add complexity to a project. New methods are required to adapt to this situation, notably to identify and improve common practices that exist across the development of a wide variety of systems. A double verification or a cross-validation alone is not enough to guarantee the success of a complex project.

Verification and validation are done throughout the creation of a new product. However, there can be multiple iterations over the process, and creating a product prototype each time for the verification adds to the cost and timescale. For example, a printed circuit board can take more than a week to be delivered. A verification of the virtual product using computer simulation has advantages in terms of cost and time. Lower costs and/or faster results make simulation an interesting tool for engineers. Thus, simulation is a major verification and validation method applied to the product lifecycle.

A simulation is generally done on a digital processing unit, e.g. a processor, and thus requires a digital model. A model is a representation of an actual object with a certain level of precision. Following the product engineering process, the simulation model is then an abstraction of the functions which are concerned. Moreover, a model level of representation depends on the underlying formalism. Using a very formal meta-model allows for precise and verifiable models.

# Motivations

Formal meta-models consist in providing a mathematically-based syntax, a comprehensive semantic. Doing so enforces replicable simulations given the same models and an identical initial state.

Discrete event simulation is a paradigm in which the temporal evolution of the simulation is led by the events. In such a simulation, events are identified by the time in future at which they are meant to happen. This contrasts with discrete time simulations, in which the time advance is fixed and steady.

Discrete event simulation has advantages in certain cases over discrete time simulation. For example, for a system in which the time constant varies from long times to very short times. In such a case, the time step chosen can be very small to be able to account for fast variations, but this will trigger unnecessary computations for steady periods. On the other hand, if the time step chosen is longer to accelerate the simulation, one can miss fast variations which can occur between two computation slots. A discrete event simulation is able to use the derivative of the variable to determine the time of next event, so intervals are set according to the rate of change.

Formalisms like Discrete Event System Specification (DEVS) allow us to modeling discrete event systems. DEVS has a formal syntax, mathematically verifiable, and strict algorithms for simulating these models. Moreover, DEVS allows for model assemblies, which are required to build complex systems and is closed under coupling, i.e. a component made of sub-components externally exhibits a behaviour which can be represented by an atomic component. DEVS is thus a strong formalism for building simulations of complex systems using a discrete event paradigm.

But when it comes to representing dynamic structure systems, DEVS extensions related to such systems have limitations. DEVS formalisms for dynamic structure systems mostly rely on predetermined architectural states. Each of these states represents a model architecture, containing components and links between components. When a transition function is triggered, the model switches from one architectural state to another. The simulation environment is then responsible for inferring the actual simulation architecture from the state evolution.

While in many cases this will be enough to represent a dynamic structural system, there are other cases in which this will be a limitation. An example of this might be multi-agent systems, such as population simulation, in which agents can be born or die at some point in the simulation. In such cases, there is no way of knowing all possible architectural states of the system before simulation. We rather require a way of representing agent creation and deletion from the system, as well as relationship evolution between agents, directly in the formalism. Another field of application is complex adaptive systems, in which the network of interactions between components of the system evolve and is able to reach net structures impossible to predict.

Moreover, having a strict approach always leads to better results. The system engineering approach provides several tools for better handling system creation, including the simulation steps. One interesting concept of system engineering is the model-driven architecture approach. Initially created for software design, model-driven architecture consists of separating the application design from the execution platform. It means that the application must be written using a platform-independent representation, and must incorporate a transformation tool able to generate an executable application for various platforms. This requires a high-level, platform-agnostic, model of the system and models of the platforms that will constitute the execution target. Then, by establishing a correspondence of the models, we establish a model that is able to run on a specific platform.

Among execution platforms, we usually find the classic software processors, nowadays constituted of multiple execution cores. Recently, enthusiasm for even more parallel platforms such as graphics processing units has arisen. This kind of device, initially designed for graphics applications where the same treatment must be operated on multiple pixels, has gained a general purpose use over recent years. When application speed and/or current consumption is critical, building an Application-Specific Integrated Circuit (ASIC) is also worth considering. ASICs consist in creating a logic circuit which realizes the exact function required, allowing for very important optimizations compared to software, which requires generalisation. However, the significant of fixed costs of such devices only makes them suitable for mass production.

In the middle of all theses lie Field-Programmable Gate Arrays (FPGAs). Not as fast as ASICs, not as flexible as processors, but faster than processors and more flexible than ASICs. The FPGA represents a very interesting execution target for applications that can benefit on-demand parallelism. FPGAs being reprogrammable logic circuits, they also benefit from unique features such as partial dynamic reconfiguration. This features consists in modifying a portion of the circuit while the remaining part continues to operate, incarnating the concept of dynamic structure change. However, partial reconfiguration of FPGAs is still lacking formal methods for handling it.

# Definition of objectives

At the time of writing, dynamic structure systems are new to modeling and simulation, and often treated without a clear methodology. They could benefit from of a system engineering approach. In this work, we are aiming to define a formal modeling approach to represent and simulate dynamic structure systems. To do so, we are going to formalize the representation of such systems into a meta-model. We will particularly focus on discrete-event models, and adopt a model-driven architecture approach.

As a first step, the meta-model, in other words, the model of the models must be defined. We need the meta-model to use the strong fondation of mathematical formalism. Moreover, we want the models we define to be free from constraints related to the execution platform. However, the definition must include the capability for dynamic structure change, which will restrict the available target platforms.

We also need to distinguish the dynamic structure behaviour from a model state evolving or being changed over time. The structure change takes place at a different level than the state change. Different components can exist in a system at one time, and exhibit the exact same internal behaviour while being in a different state. The state of the components thus represents an independent information set, which must be treated separately from the structure change.

The structure itself contains two levels of possible changes. A model structure is composed of components, which have relationships with each other. The change can be operated either on components or on connections. We will see that this differentiation has an impact on the way it is handled by the execution platform.

Concerning the components state management, it will be useful to develop the capacity to save the state of a component during simulation, or to force it into a specific state. For example, we should be able to save the current state of a component about to be deleted so that it can be restored later. Or, a component can be instantiated with different initial states depending on the general simulation state at the simulation time.

Thus, we should study different target platforms in order to understand their execution behaviour. This will enable us to make the connection between models expressed in the developed meta-model and the platforms. We will begin with a software platform as a first target. On a software platform, many constraints are flexible, such as the memory size which, to some extent, can be ignored. During this integration period, the system engineering approach will be validated for our meta-model.

As a final objective, the meta-model should be integrated into a dynamic hardware platform. With this specific platform, the constraints (space and time) of the platform should be defined. On such a level, the communication protocol and scheduling behaviour of the simulation should have been considered. The parallel nature of the platform must have been developed within our meta-model.

# Structure of the document

In this thesis, we propose an interdisciplinary work between system engineering and modeling & simulation. The scientific context and state of the art are presented in the first chapter. It details the approach of system engineering and modeling, especially for discrete event simulation and dynamically reconfigurable computing systems.

In chapter two, we propose a dynamic structure meta-model: Partial Reconfigurable Discrete Event System Specification. We detail the meta-model syntax and semantics. We present the syntax using a mathematic description at a theoretical level. Then a graphic representation of the syntax is discussed to facilitate model representation.

In the third chapter, a software platform, with object-oriented programming, is presented to support the execution of models. We introduce a simulator which is able to run models described using the meta-model defined in chapter two.

In the fourth chapter, a hardware platform specification based on FPGA is presented. The platform architecture is defined in order to match the FPGA constraints.

Finally, we draw conclusions from the results and bring future perspectives into consideration.

# CHAPTER 1 Scientific context & state of the art

## Contents

| 1.1 | Syste | em engineering and simulation                                                 | 9         |

|-----|-------|-------------------------------------------------------------------------------|-----------|

| 1.  | .1.1  | Systems and system engineering                                                | 9         |

| 1.  | .1.2  | Modeling and simulation                                                       | 11        |

| 1.  | .1.3  | Model-Driven Architecture                                                     | 12        |

| 1.  | .1.4  | Syntax and semantics                                                          | 13        |

| 1.2 | DEV   | S and its extensions                                                          | <b>14</b> |

| 1.  | .2.1  | Discrete Event System Specification                                           | 14        |

| 1.  | .2.2  | Dynamic Structure DEVS and its parallel version                               | 18        |

| 1.  | .2.3  | Dynamic DEVS and its dynamic port extension                                   | 23        |

| 1.  | .2.4  | Synthesizable DEVS                                                            | 26        |

| 1.  | .2.5  | Reconfigurable DEVS $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$ | 27        |

| 1.3 | Dyna  | amically reconfigurable computing systems                                     | 29        |

| 1.  | .3.1  | Programmable logic device                                                     | 30        |

| 1.  | .3.2  | Partial reconfiguration                                                       | 31        |

| 1.4 | Conc  | clusion                                                                       | 33        |

System engineering consists in a process with several steps. The final goal of system engineering is to avoid failures while building a system. A complex system is usually decomposed into sub-systems, which are developed separately. The well-known V-model system engineering cycle, for example, begins with the feasibility study and concept exploration. It progressively goes down by breaking the system into sub-systems, which are fully specified individually. Finally, it ascends by testing system components and assembling them to form a complete system.

During the design of a system, modeling and simulation takes an important place. When a system is made of various sub-systems, all of them must be modeled as stand-alone pieces and tested individually. When bringing them together to form the whole system, how to co-simulate the independent models together is a really complex task. Co-simulation can happen between different types of models: hardware/software, continuous/discrete, electronic/digital, etc. It can also be done between different abstraction levels.

For classic systems, where the physical materials can be modeled, a software component can represent formally the physical materials. Before the simulation, an offline verification (static program analysis) is possible for the software components. The offline verification can be done using formal languages syntactically representing the system. Before the simulation, formal methods are used as critical tools for system verification, which guarantee mathematically the system is correct. If an error is detected during the static analysis with formal methods and debug, an accident can be avoided.

The simulation is not limited to dig into the inner behavior of the system. It also looks at the interaction with a surrounding environment. In order to correctly test the system, we need to put it into its environment. It can be done by modeling the environment and simulating it together with the system. Or more directly, we can put the simulated system directly in contact with the real environment. When the system is in the real environment, the simulation must respect real-time.

For a real-time system, the actuators, physical system, and its sensors can be involved as simulated elements or as real elements in the model. As an example an aircraft stress test for its wings can contain both virtual subsystems and real subsystems. The virtual subsystem may include the control system, and the real subsystem is the airplane wing. A common practice is to model the real actuators together with the simulated physic system and sensors.

What we are interested in is dynamic structure systems, where the composition can change over time. FPGA is an integrated circuit which can change its configuration to form various logic circuits. A custom design is thus possible depending on the project. Moreover, some classes of FPGA are capable of run-time re-configuration during the execution. In this chapter, we are going to discuss three main topics: system engineering together with model-based system engineering in section 1.1, Discrete Event System Specifications and its extensions in section 1.2, and reconfigurable computing systems, especially Field-Programmable Gate Arrays (FP-GAs) in section 1.3.

# 1.1 System engineering and simulation

In this section, we will define topics of expertise which are required for the further developments. First, we will give a definition of what is a system and clarify the system engineering process. Then modeling and simulation as a part of the system engineering process will be presented. Model-driven architecture is detailed later as a system engineering approach for the software development. At last, the syntax and semantics modeling notions are defined.

## 1.1.1 Systems and system engineering

There are lots of definitions of what is a system. An earlier definition was done in the 50s by Ludwig von Bertalanffy [Von Bertalanffy 1956], who contributed to general systems theory. Von Bertalanffy outlines systems inquiry into three major domains: Philosophy, science, and technology:

"The systems view is a world-view that is based on the discipline of SYS-TEM INQUIRY. Central to systems inquiry is the concept of SYSTEM. In the most general sense, a system means a configuration of parts connected and joined together by a web of relationships. The Primer Group defines the system as a family of relationships among the members acting as a whole." Here, a system is defined as elements in standing relationship.

The International Council on Systems Engineering (INCOSE) is an organization aiming at improving the systems engineering practices and education developed in 1995. Their definition is straightforward:

"A system is a construct or collection of different elements that together produce results not obtainable by the elements alone."

A system is never with only one element inside, which mean there is a possibility to decompose the system into subsystems or include a system into a larger system.

For systems engineering, the INCOSE concept is practical and includes the concept of business:

"Systems Engineering integrates all the disciplines and specialty groups into a team effort forming a structured development process that proceeds from concept to production to operation. Systems Engineering considers both the business and the technical needs of all customers with the goal of providing a quality product that meets the user needs."

The French association of systems engineering (AFIS) gives a definition oriented toward industrial manufacture:

"The control of complex systems by manufacturers is essential to maintain and improve the positions of French and European industry in the global market for large systems, whatever the field: transport, space, defense, finance, security, health, energy... These systems involve many disciplines: mechanical engineering, electrical engineering, automatic engineering, civil engineering, software engineering, electronic engineering, chemical engineering, industrial engineering, subcontracting, production, maintenance, security... but also trade, marketing, customer relations, human factors sustainable development."

For sure, applying the system engineering concept to a complex system is interesting to ensure the success of the project. Rather than the quality, cost, delivery (QCD) approach which evaluate the results, system engineering focuses on the whole project procedure, internal communication and organization.

The well-known V-model development got this name by its V form and the final steps of its procedure: verification and validation. Even though recently a lot of projects are applying other methods such as waterfall model [Bal-aji 2012], spiral model [Boehm 1988], agile methods [Ambler 2004], etc.

Within the V-model development, reliability of the system is often done by modeling and verified by simulation. It can be a general model without coding, in some case done by experience and success stories. During the requirements and architecture step, a system with several subsystems is built. Detailed designs with each subsystem's specification are defined. Before the project moves to implementation, high-level modeling is already done.

After the implementation, during test and integration, simulation is done with different methods to ensure the subsystem is functional. Under system level verification and validation, the entire system is executed, analyzed and simulation is done on the entire system level.

The Model-Based System Engineering (MBSE) [Estefan 2007] concept was introduced by AW Wymore in 1993. It was popularized by INCOSE when it kicked off its MBSE Initiative in January 2007 [Friedenthal 2007]. The main idea is to replace the document exchange during systems engineering by creating and exploiting domain models [Friedenthal 2007].

### 1.1.2 Modeling and simulation

Modeling is building an abstraction of the real world, where changes of certain parameters are used to learn the way the system behaves. Simulation is based on a model which is built based on a real system, already existing or in the design phase. It shows the results by observing the model changes over time or in response to its environment.

As for the methodology for modeling and simulation, originally presented in 1976 [Zeigler 2000], it consists of two principal aspects:

Level of system specification - These are the levels at which we can describe how systems behave and the mechanisms that make them work the way they do.

| IVI & | M&S sets four levels of system knowledge. |                                                         |  |

|-------|-------------------------------------------|---------------------------------------------------------|--|

| Level | Name                                      | What we know at this level                              |  |

| 0     | Source                                    | What variables to measure and how to observe them       |  |

| 1     | Data                                      | Data collected from a source system                     |  |

| 2     | Generative                                | Means to generate data in a data system                 |  |

| 3     | Structure                                 | Components coupled together to form a generative system |  |

M&S sets four levels of system knowledge :

**Systems specification formalisms** - These are the types of modeling styles, such as continuous or discrete, that modelers can use to build system models.

A discrete system is one in which the state variables change only at a discrete set of points in time. A continuous system is one in which the state variables change continuously over time.

Under system theory [Zeigler 2000], *structure* – the inner constitution of a system – and *behavior* – its outer manifestations – are considered separately. For a time-based system, *behavior* and *structure* are connected by time-related parameters: the internal *structure* of a system includes its state, how one state transits to another state and the mapping between state and output. A well-defined *structure* helps to analyze and simulate its behavior.

Basic system concept considers the system as a black box, where we observe the output changing in reaction to the input event. After analysis, the output can be used to correct system input.

In this case, we can see the simulation as a closed loop system in the control theory, where results of one simulation cycle can impact the next simulation cycle.

Then, four classifications of looped simulation were proposed by Jens Eickhoff [Eickhoff 2009]: Model in the loop (MIL), Software in the loop (SIL), Processor in the loop (PIL) and Hardware in the loop (HIL). The model in the loop consists in building a model describing the behavior of the system to validate it by simulation. The model of the system is coupled to an environmental model to see if the system model meets the main requirements of the system. The software in the loop principle is to create a program that implements the model in a target language. This implementation can lead to bias due to implementation constraints of the model and language limitations. A new phase of validation and/or verification is needed to ensure semantic equivalence. A processor in the loop consists in validating the behavioral equivalence of the program after integration into the target processor. The environment remains simulated. Hardware in the loop is to use the final physical controller. The environment remains simulated but now responds in real time. The difference between PIL and HIL is [Mina 2016]: PIL is a test technique that allows designers to evaluate a controller, running in a dedicated processor or a plant which runs in an offline simulation platform. On the other side, HIL is an approach to test a plant or controller running on a digital platform which interacts with the real controller or plant.

## 1.1.3 Model-Driven Architecture

The Model-Driven Architecture (MDA) approach by Object Management Group [Object Management Group 2016], derived from Model-Driven Engineering (MDE), consists in separating the application model description from the execution platform.

A good software engineering flow offers lots of advantages. The most important advantage is to define different abstraction levels, for managing the complex applications. This brings various benefits, such as allowing the teams working on an application to be independent of the ones working on the platform, or enabling deploying an application built from a single model on various platforms.

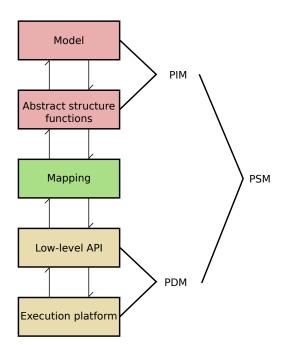

A complete MDA specification consists in a Platform-Independent Model (PIM), one or several

Figure 1.1: MDA structure of a meta-model

Platform-Dependent Models (PDM), and sets of interfaces correspondence to allow building a Platform-Specific Model (PSM) by matching a PIM with a PDM, as depicted in figure 1.1.

MDA is based on the massive use of models in all phases of the application life cycle. Standard MOF (Meta Object Facility) [Iyengar 2005] is the support for modeling formalisms under metamodel. MOF is used as the metametamodel not only for Unified Modeling Language (UML) but also for other languages, such as Common Warehouse Metamodel (CWM) [Poole 2003]. UML is defined as a model that is based on MOF. Every model element of UML is an instance of exactly one model element in MOF. A model is an instance of a metamodel. UML is a language specification (metamodel) from which users can define their own models.

With this architecture, the model can be built using different languages and translate into a unified model by mapping. In principle, an MDA is a framework for visualizing, storing and exchanging software designs and model [Kleppe 2003]. Since the framework separates the development in the first place, the PIM developers do not need to consider the platform details.

Within MDA, portability is realized by PIMs. One PIM can be deployed on multiple PSMs using different platforms PDMs. The MDA does not require a specific processes or languages for software development.

### 1.1.4 Syntax and semantics

The information and its meaning behind represent the different between syntax and semantics [Miller 1985, Dalrymple 1999, Harel 2000]. The information is represented as data while the data is the medium used to transport and store the information. There is general agreement in the literature that data is used to communicate and needs an interpretation to extract the information behind it [Harel 2000]. An interpretation is always a mapping assigning a meaning to each piece of data.

To correctly define a model, we need three levels of specification:

$\star$  An abstract syntax, or meta-model, which is the formal definition used by the modeler to define its models.

The abstract syntax is used by the modeler to build and specify the model. Model description can be done theoretically, using mathematics tools such as sets and algorithms. But the actual model description provided to the simulator is often done using a Graphical User Interface (GUI), such as the ProDEVS environment [Vu 2015], to ease the process.

$\star$  A concrete syntax, which is the actual model description matching the abstract syntax.

The concrete syntax is the way the model structure and its contents are stored and manipulated during the simulation. It must observe the abstract syntax, but its way of representing the model must be adapted to a digital representation and manipulation by the simulator. Note that this is the syntax representation which should comply with these constraints, not the model itself.

$\star$  A semantics which specifies the model execution behavior by the mean of an abstract simulator.

The abstract simulator, indicating the semantics of how the model description is to be manipulated, and how the simulator should behave when a simulation event occurs.

# **1.2** DEVS and its extensions

Discrete Event System Specification (DEVS) is a formalism to describe discrete-event models and simulate them by proposing a syntax and a semantic. A DEVS model is a hierarchical set of components of two kinds: atomic components define a behavior while coupled components gather and link other components, either atomic or coupled. The original DEVS formalism was not designed to handle structure changes, either in model composition or communication. Dynamic structure behavior can only be emulated, e.g. using a selector to enable or disable models over time. Several extensions have been proposed addressing dynamic adaptation of the models structure during the simulation.

In this section, some generic definitions and background information about Discrete Event System Specification (DEVS) and its extensions from the industry and academia are discussed.

## **1.2.1** Discrete Event System Specification

DEVS formalism introduced by Zeigler [Zeigler 2000] is a strong mathematical foundation for specifying hierarchical and modular models. The DEVS formalism allows to build discrete event systems and provides algorithms for simulation. DEVS models are made of atomic components, which define a behavior, and coupled components which can hold several other components and describe the way they are connected.

DEVS was later extended with Parallel DEVS (PDEVS), and we now reference the initial DEVS formalism as Classic DEVS (CDEVS). In this thesis, the acronym DEVS thus refers to the general DEVS ecosystem rather than to the original CDEVS formalism.

#### 1.2.1.1 Classic DEVS

Zeigler [Zeigler 2000] initially introduced the DEVS formalism in the late 70's as a way to build models with a discrete-event approach using a mathematically defined formalism.

**CDEVS atomic components syntax** CDEVS defines an atomic component as an indivisible unit implementing a behavior. It can evolve in reaction to an external event (external transition), or when a timeout occurs (internal transition). The formal definition is as follows:

$$M = \langle X, Y, S, \delta_{ext}, \delta_{int}, \lambda, \tau \rangle$$

where

- $X = \{(p, v) \mid p \in InPorts, v \in X_p\}$  is the set of input ports and values, where

- InPorts is the set of input ports

- $-X_p$  is the set of allowed input values for port p

- $Y = \{(p, v) \mid p \in OutPorts, v \in Y_p\}$  is the set of output ports and values, where

- OutPorts is the set of output ports

$- Y_p$  is the set of possible output values for p

S is the set of sequential states

$\delta_{ext} : Q \times X \to S$  is the external state transition function, where

$-Q = \{(s, e) \mid s \in S, 0 \le e \le \tau(s)\}$  is the set of total states, with e the time elapsed since latest transition

$\delta_{int} : S \to S$  is the internal state transition function

- $\lambda : S \to Y$  is the output function

- $\tau : S \to \mathbb{R}^+_{0,\infty}$  is the time advance function (sometimes referred to as ta)

As simulated time advances, the *e* variable growths. An atomic component is said to be *imminent* when its remaining time in the current state  $tr = \tau(s) - e$  is minimal among all the components in the simulation. Zeigler defines tl to be the time of the latest event that occured in the component, and  $tn = tl + \tau(s)$  the scheduled time for the next event.

It is also of use to know the component initial state, which is usually referred to as  $s_0$ .

**CDEVS coupled components syntax** A coupled component is a way of linking other components. Externally, it behaves like an atomic component and thus can be used in another coupled to form a hierarchical model.

$N = \langle X, Y, D, \{M_d\}, EIC, EOC, IC, Select > where$

X, Y as defined for atomics

D is the set of components names

$\{M_d\}$  is the set of components in this coupled, with  $d \in D$

EIC is the external input coupling function

EOC is the external output coupling function

IC is the internal coupling function.

Select:  $2^D - \{\} \to D$ , the tie-breaking function

The coupling functions define links between different components ports. They are defined as:

*EIC* links  $p_N \in InPorts_N$  to  $p_d \in InPorts_d, d \in D$

EOC links  $p_d \in OutPorts_d, d \in D$  to  $p_N \in OutPorts_N$

IC links  $p_a \in OutPorts_a, a \in D$  to  $p_b \in InPorts_b, b \in D, a \neq b$

We notice here that no direct feedback loops are allowed, i.e. no output port of a component may be connected to an input port of the same component.

The *Select* function is used when various components are simultaneously imminent. In this case, the *Select* function defines a priority for the order in which the components will be processed.

**CDEVS semantics** Zeigler defines a complete semantics for CDEVS models. An atomic component is managed by a simulator, while a coupled component is managed by a coordinator.

First, the imminence of all components is checked by the root coordinator, and a list of imminent components is established. The *Select* function is used to determine the next component to be processed if the list contains more than one component.

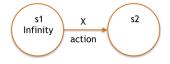

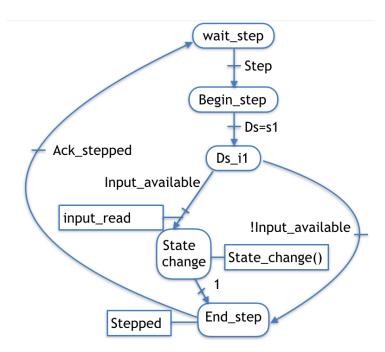

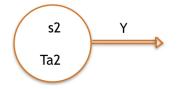

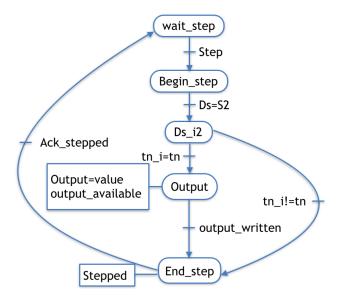

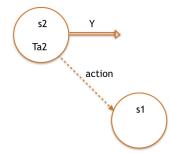

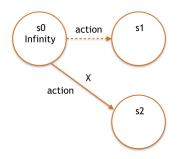

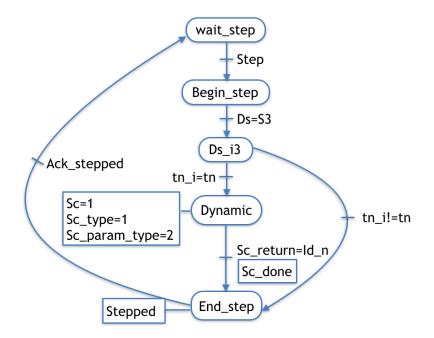

An \*-message is sent to the most imminent component simulator, which activates it. A simulator receiving an \*-message will first perform its component  $\lambda$  emission then applies its  $\delta_{int}$  internal transition.  $\lambda$  emission results in the creation of an y-message which is transmitted to its parent coordinator. Finally, the simulator updates its tl and tn internal variables.